Hello,

We have a design with a TPS71710 producing 1V from a regulated input voltage of 3V3. We use the 1V to power an ARM processor core. We have made two production (prototype and a first production). The prototypes are working correctly but the production units not. When we apply the power supply the 3V3 rise relatively slowly but the 1V rise to around 1V5 and then decrease to 1V. On the prototype the rise of the 1V is slow. We have try different value for C654 (capacitor on NR pin). It work with 100 nF but it is really big and creaste power up sequencing issue. With 10 nF it doesn't work correctly. We have also short circuit L702 but this doent' change anything. We have not find any solution. As you can see hereunder the NR pin voltage has also an overvoltage so we suspect an issue inside the integrated circuit. We know that part used for prototype were not from the same as part for production. Is it possible that TI has change somethink in the TPS71710 to correct an issue or for any other reason ?

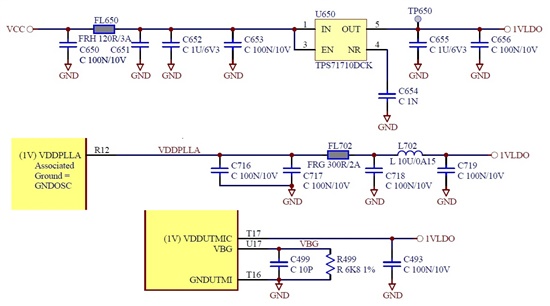

Here is the schematic

This is a copy of the scope (trace 1 is NR pin and trace 2 is LDO output voltage) with C654 of 10 nF

for the prototype (working correctly)

and a copy of the scope for the production unit (not working correctly) with C654 of 10 nF

Maybe this issue is also reltated with this one http://e2e.ti.com/support/power_management/linear_regulators/f/321/t/148668.aspx but I am unable to disconnect the load (BGA soldered on the same PCB). So I have not yet found a solution.

Thanks in advance for your help